# SEMIKRDN innovation+service

### Technical Explanation SEMITRANS10MLI M7 Driver Board

| Revision:    | 00           |

|--------------|--------------|

| Issue date:  | 2021-01-25   |

| Prepared by: | Joachim Lamp |

| Reviewed by: | -            |

| Approved by: | Ingo Rabl    |

Keyword: SEMITRANS10, MLI, IGBT driver, Application Sample, M7, 451579

| 1.1       Features       2         1.2       Hardware of the SEMITRANS10 MLI M7 Driver Board       3         2.       Safety Instructions       3         2.       Safety Instructions       5         3.       Technical Data       7         3.1       Driver Kit block diagram       7         3.2       Electrical and mechanical characteristics       7         3.3       Integrated functions       8         3.3.1       Thermal protection       8         3.3.2       Active clamping       9         3.4.1       Adjustment of temperature error       9         3.4.2       Gate resistors       11         3.4.3       Gate-Emitter (GE) components       11         3.4.4       Active clamping       12         3.4.5       Filter for V <sub>CE</sub> detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       13         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse                                                                               | 1. Introduction                                     | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----|

| 2. Safety Instructions       5         3. Technical Data       7         3.1 Driver Kit block diagram       7         3.2 Electrical and mechanical characteristics       7         3.3 Integrated functions       8         3.3.1 Thermal protection       8         3.3.2 Active clamping       9         3.4 Board description       9         3.4.1 Adjustment of temperature error       9         3.4.2 Gate resistors       11         3.4.3 Gate-Emitter (GE) components       11         3.4.4 Active clamping       11         3.4.5 Filter for V <sub>CE</sub> detection       12         3.4.6 Power supply boost capacitors       12         3.4.7 Error management       13         3.4.8 Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9 Input short circuit detection       18         5.1 With short circuit detection       18         5.2 Without short circuit detection       18         5.3 Error treatment in paralleled drivers       19         5.4 Error treatment in paralleled drivers       19         5.5 Design limits gate resistors       19<    |                                                     |    |

| 3. Technical Data       7         3.1 Driver Kit block diagram.       7         3.2 Electrical and mechanical characteristics       7         3.3 Integrated functions       8         3.3.1 Thermal protection       8         3.3.2 Active clamping       9         3.4 Board description       9         3.4.1 Adjustment of temperature error       9         3.4.2 Gate resistors       11         3.4.3 Gate-Emitter (GE) components       11         3.4.4 Active clamping       11         3.4.5 Filter for V <sub>CE</sub> detection       12         3.4.6 Power supply boost capacitors       12         3.4.7 Error management       13         3.4.8 Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.8 Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and Briver T3/T4       14         3.4.8 User interface       15         4.1 Module interface       15         4.2 User interface       15         5.1 With short circuit detection       18         5.3 Error treatment in paralleled drivers       < | 1.2 Hardware of the SEMITRANS10 MLI M7 Driver Board | 3  |

| 3. Technical Data       7         3.1 Driver Kit block diagram.       7         3.2 Electrical and mechanical characteristics       7         3.3 Integrated functions       8         3.3.1 Thermal protection       8         3.3.2 Active clamping       9         3.4 Board description       9         3.4.1 Adjustment of temperature error       9         3.4.2 Gate resistors       11         3.4.3 Gate-Emitter (GE) components       11         3.4.4 Active clamping       11         3.4.5 Filter for V <sub>CE</sub> detection       12         3.4.6 Power supply boost capacitors       12         3.4.7 Error management       13         3.4.8 Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.8 Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9 Input pulse filtering driver T1/T2 and Briver T3/T4       14         3.4.8 User interface       15         4.1 Module interface       15         4.2 User interface       15         5.1 With short circuit detection       18         5.3 Error treatment in paralleled drivers       < | 2. Safety Instructions                              | 5  |

| 3.1       Driver Kit block diagram.       7         3.2       Electrical and mechanical characteristics       7         3.3       Integrated functions       8         3.3.1       Thermal protection       8         3.3.2       Active clamping       9         3.4       Board description       9         3.4.1       Adjustment of temperature error       9         3.4.2       Gate resistors       11         3.4.3       Gate-Emitter (GE) components       11         3.4.4       Active clamping       11         3.4.5       Filter for VCE detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       13         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         4. User Interface       15         4.1       Module interface       15         4.2       User interface       15         5.1       Without short circuit detection       18         5.2       Without short circuit detection       18         5.3       Error treatment in paralleled drivers       18                                                                                              | 2 Technical Data                                    | 7  |

| 3.2       Electrical and mechanical characteristics       7         3.3       Integrated functions       8         3.3.1       Thermal protection       8         3.3.2       Active clamping       9         3.4       Board description       9         3.4.1       Adjustment of temperature error       9         3.4.2       Gate resistors       11         3.4.3       Gate-Emitter (GE) components       11         3.4.4       Active clamping       11         3.4.5       Filter for V <sub>CE</sub> detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       12         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         4. User Interface       15         4.1       Module interface       15         4.2       User interface       15         5.4       Module short circuit detection       18         5.4       Error treatment in paralleled drivers       18         5.4       Error treatment in 3-phase systems       19         5.5.1       Minimum gate resistors       19<                                                                               |                                                     |    |

| 3.3       Integrated functions       8         3.3.1       Thermal protection       8         3.3.2       Active clamping       9         3.4       Board description       9         3.4.1       Adjustment of temperature error       9         3.4.2       Gate resistors       11         3.4.3       Gate-Emitter (GE) components       11         3.4.4       Active clamping       11         3.4.5       Filter for V <sub>CE</sub> detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       13         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         4.       User Interface       15         4.1       Module interface       15         4.2       User interface       15         5.3       Kith short circuit detection       18         5.4       With out short circuit detection       18         5.3       Error treatment in paralleled drivers       18         5.4       Error treatment in                                                                                |                                                     |    |

| 3.3.1       Thermal protection       8         3.3.2       Active clamping       9         3.4       Board description       9         3.4.1       Adjustment of temperature error       9         3.4.2       Gate resistors       11         3.4.3       Gate-Emitter (GE) components       11         3.4.4       Active clamping       11         3.4.5       Filter for V <sub>CE</sub> detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       13         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         4. User Interface       15       15         4.1       Module interface       15         4.2       User interface       16         5.2       With short circuit detection       18         5.3       Error treatment in 3-phase systems       19         5.5       Design limits gate resistors       19         5.5.1       Minimum gate resistors       19         5.5       Design limits sarb                                                                               |                                                     |    |

| 3.3.2Active clamping93.4Board description93.4.1Adjustment of temperature error93.4.2Gate resistors113.4.3Gate-Emitter (GE) components113.4.4Active clamping113.4.5Filter for $V_{CE}$ detection123.4.6Power supply boost capacitors123.4.7Error management133.4.8Interlock time of driver T1/T2 and driver T3/T4143.4.9Input pulse filtering driver T1/T2 and driver T3/T4143.4.9Input pulse filtering driver T1/T2 and driver T3/T4144.User Interface154.1Module interface154.1Module interface155.1With short circuit detection185.2Without short circuit detection185.3Error treatment in aralleled drivers195.5Design limits gate resistors195.5.1Minimum gate resistors195.5Design limits active clamping195.6Design limits active clamping195.7Design limits active clamping195.8Design limits active clamping195.9Design limits active clamping195.1Besign limits active clamping195.4Design limits active clamping195.5Design limits active clamping195.6Design limits active clamping195.7Design limits                                                                                                                                                                                                                                               |                                                     |    |

| 3.4       Board description       9         3.4.1       Adjustment of temperature error       9         3.4.2       Gate resistors       11         3.4.3       Gate-Emitter (GE) components       11         3.4.4       Active clamping       11         3.4.5       Filter for V <sub>CE</sub> detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       13         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         4.       User Interface       15         4.1       Module interface       15         4.2       User interface       15         4.2       User interface       16         5.1       With short circuit detection       18         5.2       Without short circuit detection       18         5.4       Error treatment in 3-phase systems       19         5.5       Design limits gate resistors       19         5.5.1       Minimum gate resistors       19         5.5.2       Power rat                                                                               |                                                     |    |

| 3.4.1Adjustment of temperature error.93.4.2Gate resistors.113.4.3Gate-Emitter (GE) components.113.4.4Active clamping.113.4.5Filter for V <sub>CE</sub> detection.123.4.6Power supply boost capacitors.123.4.7Error management.133.4.8Interlock time of driver T1/T2 and driver T3/T4.133.4.9Input pulse filtering driver T1/T2 and driver T3/T4.144.0User Interface.154.1Module interface.154.2User interface.154.2User interface.175.Recommended settings and restrictions185.1With short circuit detection.185.2Without short circuit detection.185.3Error treatment in paralleled drivers.185.4Error treatment in 3-phase systems.195.5Design limits gate resistors.195.5.2Power rating of the gate resistors.195.6Design limits active clamping.195.7Design limits active clamping.195.8Design limits ambient temperature.195.8Design limits ambient temperature.19                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |    |

| 3.4.3       Gate-Emitter (GE) components       11         3.4.4       Active clamping       11         3.4.5       Filter for VCE detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       13         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         4.       User Interface       15         4.1       Module interface       15         4.2       User Interface       17         5.       Recommended settings and restrictions.       18         5.1       With short circuit detection       18         5.2       Without short circuit detection       18         5.4       Error treatment in 3-phase systems       19         5.5       Design limits gate resistors       19         5.5.1       Minimum gate resistors       19         5.2       Power rating of the gate resistors       19         5.5       Design limits active clamping       19         5.6       Design limits active clamping       19         5.7       Design limits ambient temperature       19         5                                                                                |                                                     |    |

| 3.4.4Active clamping113.4.5Filter for $V_{CE}$ detection123.4.6Power supply boost capacitors123.4.7Error management133.4.8Interlock time of driver T1/T2 and driver T3/T4143.4.9Input pulse filtering driver T1/T2 and driver T3/T4144.User Interface154.1Module interface154.2User interface155.Recommended settings and restrictions185.1With short circuit detection185.3Error treatment in paralleled drivers185.4Error treatment in 3-phase systems195.5Design limits gate resistors195.6Design limits active clamping195.7Design limits active clamping195.8Design limits ambient temperature195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |    |

| 3.4.5       Filter for V <sub>CE</sub> detection       12         3.4.6       Power supply boost capacitors       12         3.4.7       Error management       13         3.4.8       Interlock time of driver T1/T2 and driver T3/T4       14         3.4.9       Input pulse filtering driver T1/T2 and driver T3/T4       14         4.       User Interface       15         4.1       Module interface       15         4.2       User interface       15         4.2       User interface       16         5.1       With short circuit detection       18         5.2       Without short circuit detection       18         5.3       Error treatment in paralleled drivers       18         5.4       Error treatment in 3-phase systems       19         5.5       Design limits gate resistors       19         5.6       Design limits active clamping       19         5.7       Design limits active clamping       19         5.7       Design limits active clamping       19         5.8       Design limits ambient temperature       19                                                                                                                                                                                                    |                                                     |    |

| 3.4.6Power supply boost capacitors123.4.7Error management133.4.8Interlock time of driver T1/T2 and driver T3/T4143.4.9Input pulse filtering driver T1/T2 and driver T3/T4144.User Interface154.1Module interface154.2User interface155.Recommended settings and restrictions.185.1With short circuit detection185.2Without short circuit detection185.3Error treatment in paralleled drivers195.5Design limits gate resistors195.5.1Minimum gate resistors195.5Design limits active clamping195.7Design limits active clamping195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |    |

| 3.4.7Error management133.4.8Interlock time of driver T1/T2 and driver T3/T4143.4.9Input pulse filtering driver T1/T2 and driver T3/T4144.User Interface154.1Module interface154.2User interface175.Recommended settings and restrictions185.1With short circuit detection185.2Without short circuit detection185.3Error treatment in paralleled drivers185.4Error treatment in 3-phase systems195.5.1Minimum gate resistors195.5.2Power rating of the gate resistors195.6Design limits active clamping195.7Design limits switching frequency195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |    |

| 3.4.8Interlock time of driver T1/T2 and driver T3/T4143.4.9Input pulse filtering driver T1/T2 and driver T3/T4144.User Interface154.1Module interface154.2User interface154.2User interface175.Recommended settings and restrictions185.1With short circuit detection185.2Without short circuit detection185.3Error treatment in paralleled drivers185.4Error treatment in 3-phase systems195.5Design limits gate resistors195.6Design limits active clamping195.7Design limits switching frequency195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |    |

| 3.4.9 Input pulse filtering driver T1/T2 and driver T3/T4144. User Interface154.1 Module interface154.2 User interface175. Recommended settings and restrictions185.1 With short circuit detection185.2 Without short circuit detection185.3 Error treatment in paralleled drivers185.4 Error treatment in 3-phase systems195.5 Design limits gate resistors195.6 Design limits active clamping195.7 Design limits switching frequency195.8 Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |    |

| 4. User Interface       15         4.1 Module interface       15         4.2 User interface       17         5. Recommended settings and restrictions       18         5.1 With short circuit detection       18         5.2 Without short circuit detection       18         5.3 Error treatment in paralleled drivers       18         5.4 Error treatment in 3-phase systems       19         5.5 Design limits gate resistors       19         5.5.1 Minimum gate resistor       19         5.5.2 Power rating of the gate resistors       19         5.6 Design limits active clamping       19         5.7 Design limits switching frequency       19         5.8 Design limits ambient temperature       19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |    |

| 4.1Module interface154.2User interface175.Recommended settings and restrictions185.1With short circuit detection185.2Without short circuit detection185.3Error treatment in paralleled drivers185.4Error treatment in 3-phase systems195.5Design limits gate resistors195.5.1Minimum gate resistor195.5.2Power rating of the gate resistors195.6Design limits active clamping195.7Design limits switching frequency195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |    |

| 4.2User interface175.Recommended settings and restrictions185.1With short circuit detection185.2Without short circuit detection185.3Error treatment in paralleled drivers185.4Error treatment in 3-phase systems195.5Design limits gate resistors195.5.1Minimum gate resistor195.5.2Power rating of the gate resistors195.6Design limits active clamping195.7Design limits switching frequency195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |    |

| 5. Recommended settings and restrictions.       18         5.1 With short circuit detection       18         5.2 Without short circuit detection       18         5.3 Error treatment in paralleled drivers       18         5.4 Error treatment in 3-phase systems       19         5.5 Design limits gate resistors       19         5.5.1 Minimum gate resistor       19         5.5.2 Power rating of the gate resistors       19         5.6 Design limits active clamping       19         5.7 Design limits switching frequency       19         5.8 Design limits ambient temperature       19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     | -  |

| 5.1With short circuit detection185.2Without short circuit detection185.3Error treatment in paralleled drivers185.4Error treatment in 3-phase systems195.5Design limits gate resistors195.5.1Minimum gate resistor195.5.2Power rating of the gate resistors195.6Design limits active clamping195.7Design limits switching frequency195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2 User interface                                  | 17 |

| 5.1With short circuit detection185.2Without short circuit detection185.3Error treatment in paralleled drivers185.4Error treatment in 3-phase systems195.5Design limits gate resistors195.5.1Minimum gate resistor195.5.2Power rating of the gate resistors195.6Design limits active clamping195.7Design limits switching frequency195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5. Recommended settings and restrictions            | 18 |

| 5.3 Error treatment in paralleled drivers185.4 Error treatment in 3-phase systems195.5 Design limits gate resistors195.5.1 Minimum gate resistor195.5.2 Power rating of the gate resistors195.6 Design limits active clamping195.7 Design limits switching frequency195.8 Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |    |

| 5.4Error treatment in 3-phase systems.195.5Design limits gate resistors.195.5.1Minimum gate resistor195.5.2Power rating of the gate resistors.195.6Design limits active clamping.195.7Design limits switching frequency.195.8Design limits ambient temperature.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.2 Without short circuit detection                 | 18 |

| 5.5 Design limits gate resistors.195.5.1 Minimum gate resistor195.5.2 Power rating of the gate resistors.195.6 Design limits active clamping.195.7 Design limits switching frequency.195.8 Design limits ambient temperature.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |    |

| 5.5.1Minimum gate resistor195.5.2Power rating of the gate resistors195.6Design limits active clamping195.7Design limits switching frequency195.8Design limits ambient temperature19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |    |

| 5.5.2 Power rating of the gate resistors.195.6 Design limits active clamping.195.7 Design limits switching frequency.195.8 Design limits ambient temperature.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |    |

| <ul> <li>5.6 Design limits active clamping</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |    |

| <ul> <li>5.7 Design limits switching frequency</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |    |

| 5.8 Design limits ambient temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                   |    |

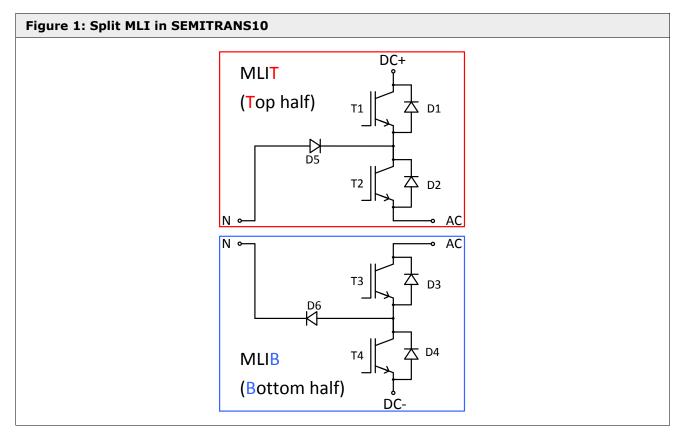

#### 1. Introduction

Beside the already existing driver board for SEMITRANS10 (ST10) 1200V MLI in Trench 4 (E4) technology SEMIKRON set up a driver board for operating Generation 7 (M7) modules for evaluation purposes. The SEMITRANS10 MLI M7 Driver Board ("driver board") is able to operate the module up to a DC-link voltage of 1500V (limited by insulation coordination) at a maximum switching frequency of 30kHz for the ST10 MLI M7 modules (limited by insulation coordination); i.e. higher switching frequencies are possible with a revision of the insulation coordination and the limitation of the gate driver needs to be taken into account.

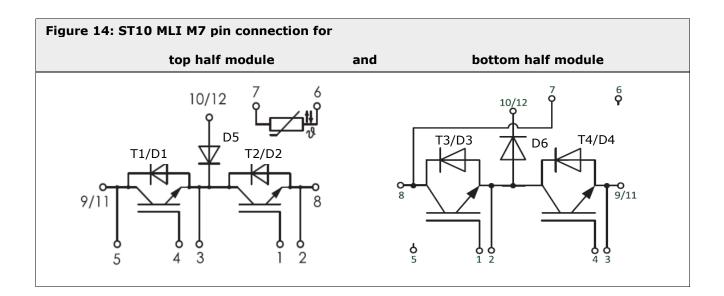

Two standard 2L drivers (SKYPER 42 LJ PV) are used to operate the 3L MLI module; one driver operates switches T1 and T2, the other operates switches T3 and T4.

The failure management of the two SKYPER 42 LJ PV drivers detects desaturation events at all four switches (IGBTs T1 to T4). The built-in temperature sensor is monitored on T1. The error management is set, that desaturation of any switch leads to an immediate shut-off of the particular IGBTs and produces an error signal. In this case all other IGBTs are immediately switched off by the linked error signal. The active clamping prevents voltage overload on IGBTs and allows to switch off IGBTs at any time without the need to follow a special switch off regime as it is usually required for MLI application.

In case the built-in temperature sensor exceeds a set temperature (can be set by user) the IGBTs are turned off immediately and the driver produces an error signal.

However, the error management can be changed by SKYPER's resistor settings to MLI mode. Means that the particular driver generates an error signal when a secondary side error occurs, but the concerned IGBTs are not turned off. The driver does not react to an external error signal; it stays in the previous state until it is turned off by PWM. See Error management 3.4.7

Please see Technical Explanation "Gate Driver Configuration and Short Circuit Protection for 3-Level Topologies" [8]

This Application Sample is dedicated to both universities and professional development engineers. It offers an easy way to set up high power inverters with standard MLI modules and 2L drivers. Performance tests can be run to prove the possibility of operation at high DC-link voltages and high output power.

#### 1.1 Features

The SEMITRANS10 MLI M7 Driver Board is designed for the SKM1400MLI12TM7 (top half module) and SKM1400MLI12BM7 (bottom half module). Both are rated 1400A and come with 1200V Generation 7 IGBTs.

In comparison to the modules in Trench 4 technology (SKM1200MLI12TE4 and SKM1200MLI12BE4), the modules in Generation 7 technology feature instead of temperature sensor on IGBT T3 a collector sensing auxiliary contact. Hence, the temperature is detected at IGBT T1 only.

The used driver core SKYPER® 42 LJ PV (L5073102) features a max. DC-Link voltage capability of up to 1500V for photovoltaic application and 35A peak current.

#### Figure 2: SEMITRANS10

It is the most powerful MLI module in the SEMITRANS10 housing.

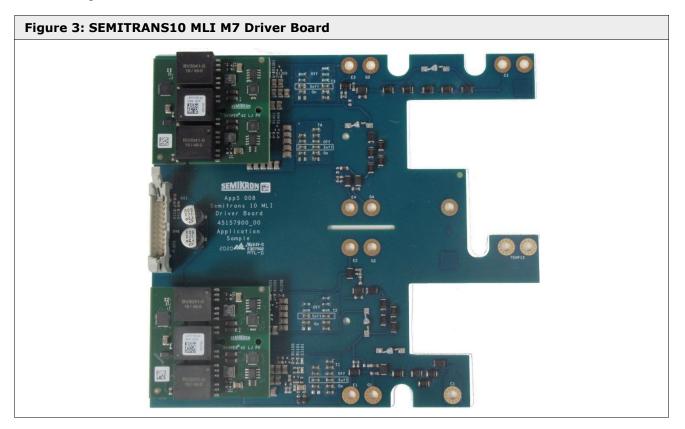

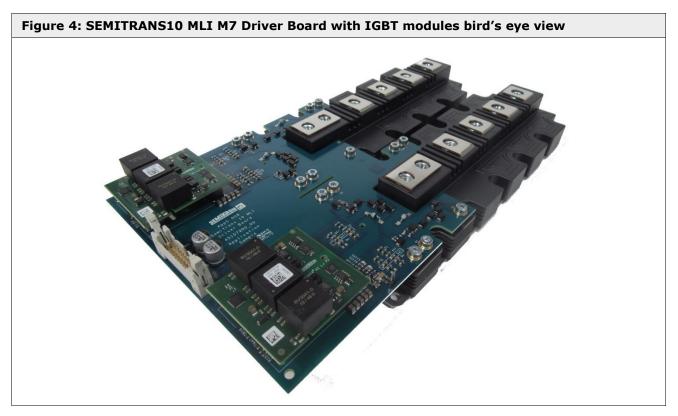

#### 1.2 Hardware of the SEMITRANS10 MLI M7 Driver Board

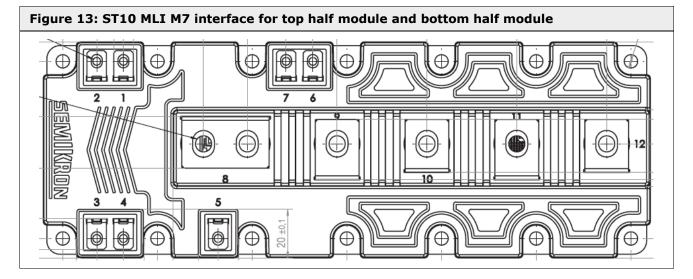

The SEMITRANS10 MLI M7 Driver Board consists of a printed circuit board (PCB): it is called "SEMITRANS 10 MLI M7 Driver Board" ("driver board"; containing gate resistors, clamping circuitry, etc.) with item number 45157901. It contacts the SEMITRANS10 modules and provides sockets for the SKYPER 42 LJ PV drivers and a user interface.

The driver board is designed for 4mm distance between ST10 module housings. So the mounting hole distance between both modules is 20mm measured from top module right mounting hole to bottom module left mounting hole.

The SEMITRANS10 MLI M7 module may be chosen according to the desired current and voltage rating.

Depending on the power rating and the operating conditions (voltage, current, inductance of the DC-link connection) it might be necessary to adjust gate resistors, clamping voltage and trip levels of the safety circuits.

The Gerber files of the board are available on request. For ordering the board or the files please contact your SEMIKRON sales partner.

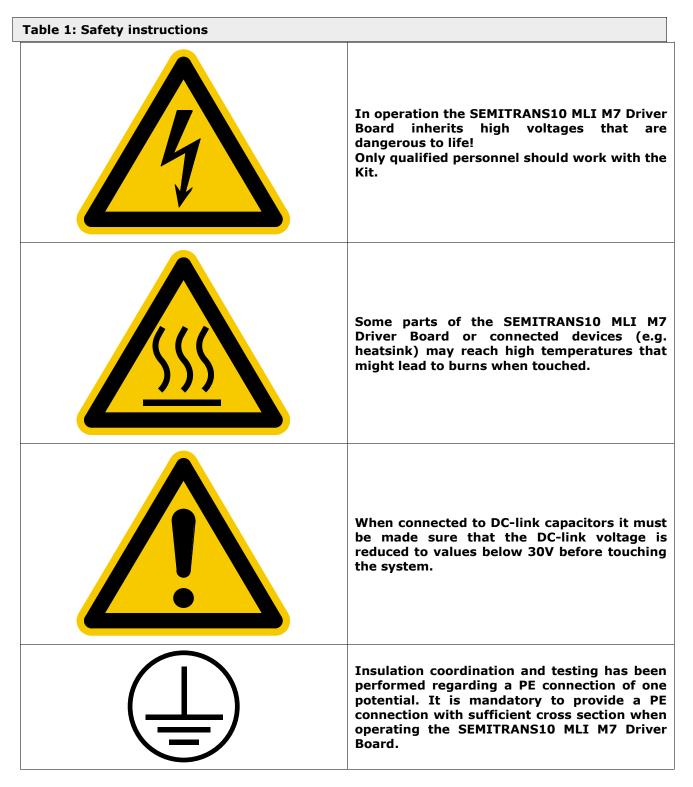

#### 2. Safety Instructions

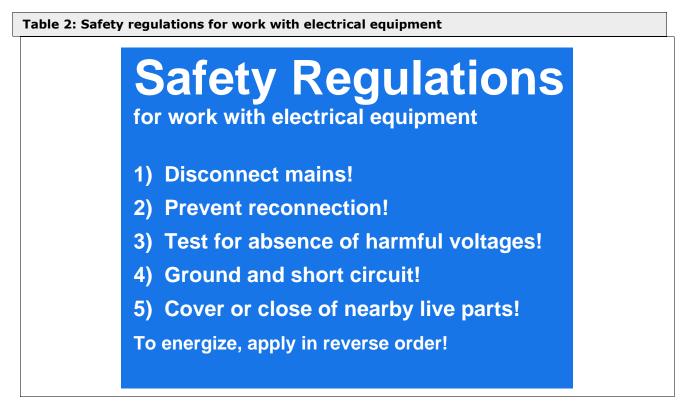

The SEMITRANS10 MLI M7 Driver Board bares risks when put in operation. Please carefully read and obey the following safety instructions to avoid harm or damage to persons or gear.

Please follow the safety regulations for working safe with the SEMITRANS10 MLI M7 Driver Board.

Operating the Application Sample may go along with electromagnetic fields which may disturb cardiac devices.

People with cardiac devices shall not operate the device.

#### 3. Technical Data

#### 3.1 Driver Kit block diagram

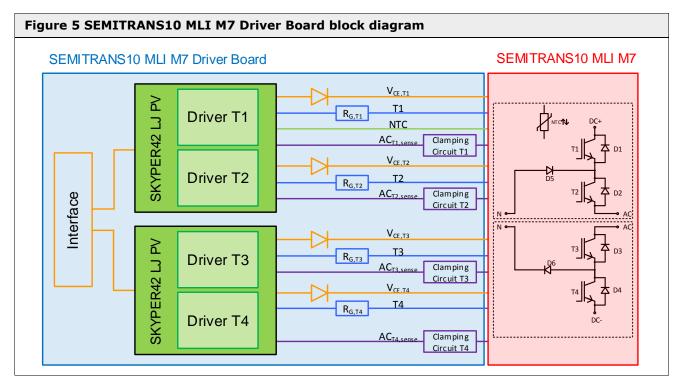

The electrical block diagram in Figure 5 shows two parts: the blue marked part is the driver PCB with sockets for the two SKYPER 42 LJ PV drivers (green), gate resistors, clamping, thermal protection and  $V_{CE}$  sensing circuitry. The red part symbolizes the 3-level module.

#### 3.2 Electrical and mechanical characteristics

With regard to the requirement specification the SEMITRANS10 MLI M7 Driver Board allows for operation within the following boundaries:

- Max. DC-link voltage

- Max. AC voltage

- Max. switching frequency

- Ambient temperature

CTI rating of AppS PCBs

- $V_{\text{DC}}$  = 1500V in total, max. 750V per individual DC-link half

- $V_{AC} = 1000V_{RMS}$  (line-to-line)

- $f_{sw} = 30$ kHz (see chapter 5.7 for further information)

- $T_a = 0^{\circ}C...40^{\circ}C$  (see chapter 5.8 for further information)

- > 175

- Neglecting the above mentioned boundaries may lead to malfunction or damage of the SEMITRANS10 MLI M7 Driver Board.

An electrical insulation is implemented between the user interface (primary side) and the high voltage connections (secondary side) by using the SKYPER 42 LJ PV's separation. The creepage distance on the driver board is 30mm and the clearance distance is 29mm between primary and secondary side.

The overall responsibility for a proper insulation coordination remains with the user.

## Please note that further restrictions of the used driver (e.g. SKYPER 42 LJ PV) may apply. According information can be found in the technical documentation of the particular driver (e.g. Technical Explanations on the SEMIKRON website [1]).

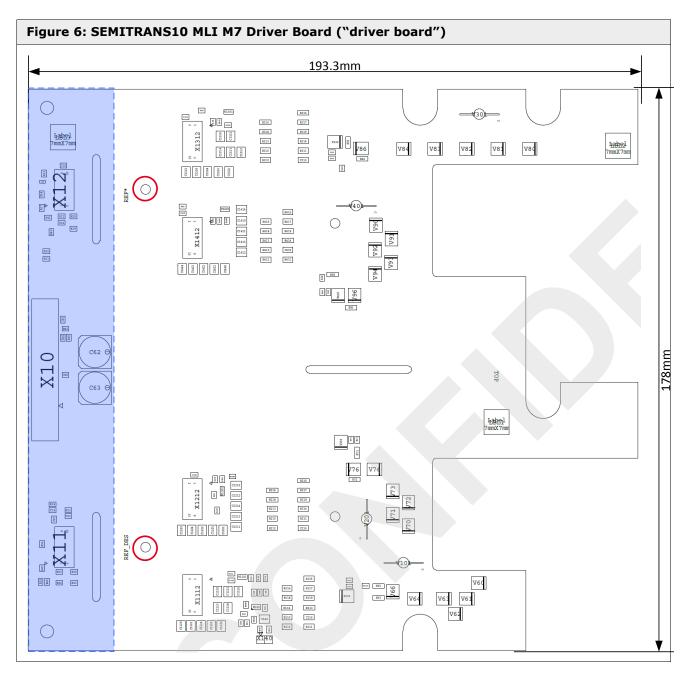

The driver board is 193.3mm long and 178.mm wide. Including SKYPER 42 LJ PV drivers it adds a total height to the modules of 28.5mm.

To prevent the driver board and the SKYPER 42 LJ PV drivers from loosening from each other mounting holes for dual lock support posts are available (positions circled red in Figure 6). Please find further information in the technical explanation of SKYPER 42 LJ PV [6].

The driver board can be mounted to the SEMITRANS10 modules by using M4 screws and washers. Further information on maximum length of the screw and mounting torque can be found in the Mounting Instruction of SEMITRANS10 [1]. Before mounting the driver board the SEMITRANS10 modules need to be mounted to the heatsink. Information how to do so is also given in the SEMITRANS10 Mounting Instruction.

The blue marked area in Figure 6 indicates the primary side with the user interface socket. The insulation is provided by the galvanic insulation of the SKYPER 42 LJ PV drivers and the insulation gap on the driver board. All area besides the blue marking may be considered as high voltage area (secondary side).

#### 3.3 Integrated functions

The driver board has some integrated safety functions to protect the device from certain harmful conditions.

#### 3.3.1 Thermal protection

The SEMITRANS10 modules' built-in NTC temperature sensors are monitored by the error input of IGBT T1. At a pre-defined temperature (to be defined by the user by adjusting a resistor) T1 is switched off immediately and the error is transmitted from secondary side to primary side by the driver. In this case all other IGBTs are immediately switched off by the linked error signal Desaturation detection.

The voltage drop across all IGBTs T1 to T4 is measured while conducting. As soon as the voltage rises above a pre-defined value (that correlates to very high current of a desaturation event) an error message is generated.

#### 3.3.2 Active clamping

All switches (T1 to T4) are protected versus over voltage by active clamping. The clamping circuit's protection level shall be chosen to a value that does not affect the device in normal operation. At the same time the level should be low enough not to exceed the blocking voltage.

When active clamping comes in action the output stage of the SKYPER 42 LJ PV is switched off in order not to work against the active clamping.

#### 3.4 Board description

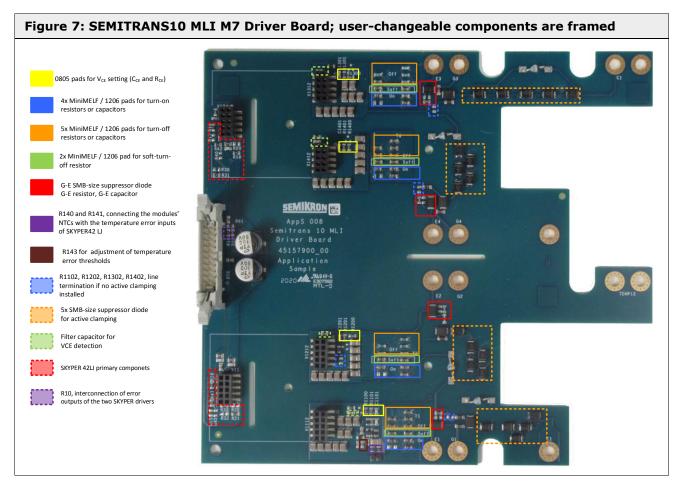

The board comes along w/o gate resistors and active clamping diodes. The components need to be selected by the user according to the application conditions and DC-link design. Several mounted components are meant to be changed. The changeable components of the driver board are marked with different coloured frames in Figure 7; function and possible values are explained in chapters 3.4.1 to 3.4.4.

#### 3.4.1 Adjustment of temperature error

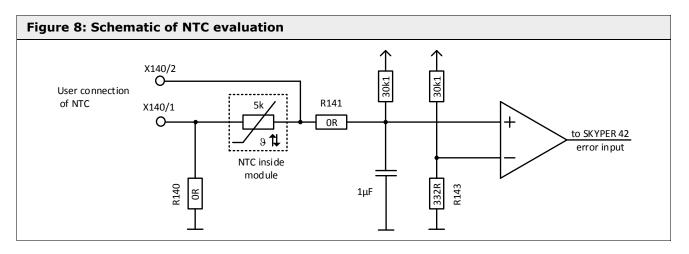

A thermal overload can be detected on both modules by evaluating the ST10 module's built-in NTC sensor. In case a thermal overload is detected the comparator shown in Figure 8 pulls the SKYPER's error input to GND and so the driver can communicate an error message.

The resistor R143 for top half module (framed brown in Figure 7 ) can be used for adjusting the error temperature threshold.

The standard value for R143 is  $332\Omega$  (refers to a junction temperature of 116°C): The thermal overload detection is deactivated by leaving R140 and R141 unpopulated.

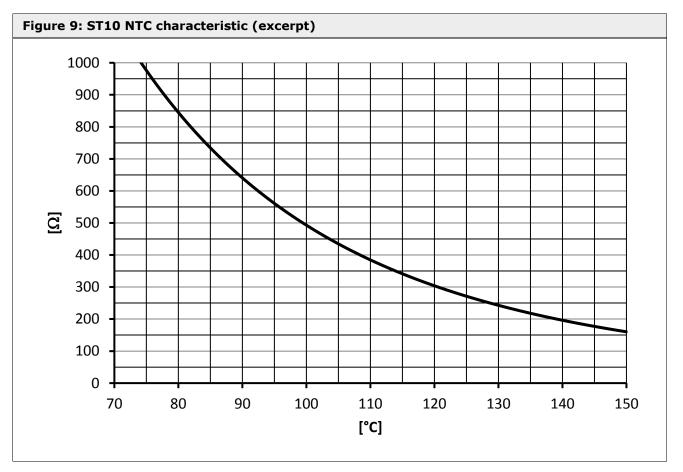

An error is detected, when the voltage at the inverting input of the comparator is greater than the voltage at the non-inverting input. The resistance of the NTC at a desired shut-off temperature can be taken from the diagram in Figure 9; R143 needs to be chosen to that value. A chip resistors with the size 0805 can be used for R143.

It is possible to use a separate, user-specific thermal detection; in this case resistors R140 and R141 must be removed.

Figure 9 shows an excerpt of the ST10 NTC characteristic which includes the most interesting temperature range between 70°C and 150°C. The full characteristic can be found in the Technical Explanation or can be calculated from the formula given in the ST10 datasheets [1].

#### 3.4.2 Gate resistors

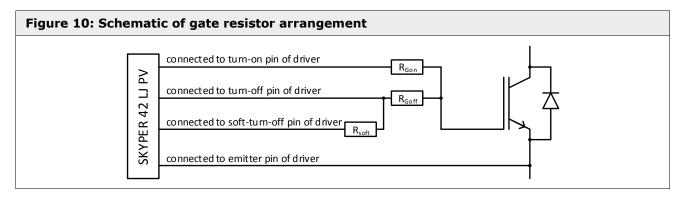

What is called gate resistor in this document for the sake of convenience is realized by three resistors on the contact board. The SKYPER 42 LJ PV offers separate connections for turn-on ( $R_{Gon}$ ), turn-off ( $R_{Goff}$ ) and soft-turn-off ( $R_{soft}$ ), see Figure 10.  $R_{Gon}$  is used for every turn-on process,  $R_{Goff}$  for every turn-off action. In case of an error the driver uses  $R_{soft}$  instead of the standard  $R_{Goff}$ . All resistor positions must be populated for proper operation.

An additional resistor between driver and the emitters of the paralleled modules reduces oscillations during switching.

#### Turn-on resistor (R<sub>Gon</sub>) / capacitor

The driver board offers four pads per IGBT (framed blue in Figure 7) taking MiniMELF or 1206 sized components. Resistor/capacitor values need to be chosen according to the particular application (DC-link voltage, DC-link inductance, switching frequency, switching losses, etc.) so there is no general recommendation.

It is necessary to calculate the power losses of the gate resistor in order not to overload and damage it. Please refer to chapter 5.5 for further information.

#### Turn-off resistor (R<sub>Goff</sub>) / capacitor

The driver board offers five pads per IGBT (framed orange in Figure 7) taking MiniMELF or 1206 sized components. Resistor/capacitor values need to be chosen according to the particular application (DC-link voltage, DC-link inductance, switching frequency, switching losses, etc.) so there is no general recommendation. It is necessary to calculate the power losses of the gate resistor in order not to overload and damage it.

Please refer to chapter 5.5 for further information.

#### Soft-turn-off resistor (R<sub>soft</sub>)

The driver board offers two pads per IGBT (framed green in Figure 7) taking a MiniMELF or 1206 sized component. The resistor values need to be chosen according to the particular application (DC-link voltage, DC-link inductance, switching frequency, switching losses, etc.).

It is recommended to calculate the power losses of the gate resistor in order not to overload and damage it. Please refer to chapter 5.5 for further information.

#### **3.4.3 Gate-Emitter (GE) components**

For every IGBT the contact board offers one pad sized SMB and two pads sized 0805 (framed red in Figure 7). SEMIKRON recommends to use one of the 0805 sized pads for placing a  $10k\Omega$  resistor and the SMB sized pad for placing a 15V bidirectional breakdown-diode for gate protection. The additional 0805 sized pad may be used for a GE capacitor if required.

#### 3.4.4 Active clamping

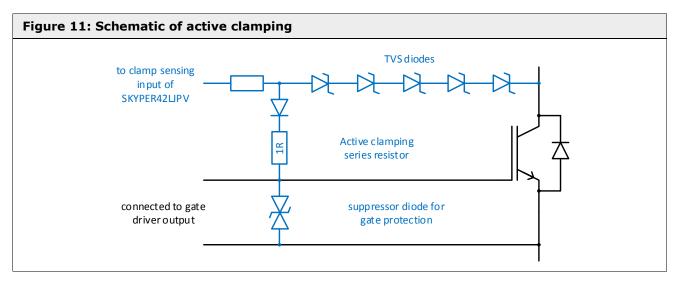

Figure 11 shows the schematic of the active clamping used in the Application Sample. The driver board offers five pads sized SMB per IGBT (V60-V64, V70-V74, V80-V84 and V90-V94 framed dotted brown in Figure 7) for placing TVS diodes (transient voltage suppressor diodes). Additionally to the TVS diodes a resistor (R63, R71, R81, R91) limits the current charging the gate and a suppressor diode protects the gate from too high voltages. A standard diode (V66, V76, V86, V96) prevents the driver from feeding into the collector in standard operation. Further the chain of TVS diode is connected to the clamping input of the SKYPER 42 LJ

PV via a resistor. In case of a clamping event the driver stage is disconnected from the gate so that the gate charging effect of the active clamping and the driver don't work against each other.

Please refer to chapter 5.6 for further information.

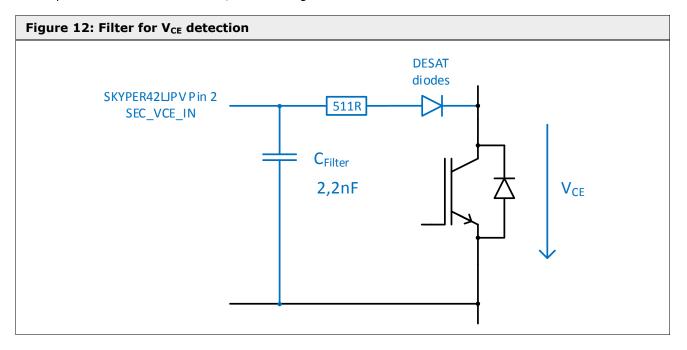

#### 3.4.5 Filter for V<sub>CE</sub> detection

Figure 12 shows the schematic for the filtering of the IGBT collector-emitter voltage  $V_{CE}$  (filter capacitor framed dotted green in Figure 7).

The filtering of IGBT collector-emitter voltage may be needed especially for inner IGBTs T2 and T3 to prevent spurious desaturation detection.

Explanation: T1 is switching on while T2 has already been switched on. Blanking time on T2 is over. A high load di/dt (e.g. capacitive load) can lead to a voltage spike on T2's and T3's Vce detection. This might lead to spurious triggering of desaturation detection. To prevent this triggering the voltage spike can be filtered. The explanation is also valid for T3/T4 switching.

#### 3.4.6 Power supply boost capacitors

The board is equipped with  $50\mu$ F boost capacitors on secondary side power supply to stabilize the gate voltages VG(on) and VG(off) during the semiconductor switching.

#### 3.4.7 Error management

#### **Error interconnection of SKYPER 42 LJ PV drivers**

The 0805 sized R10 (framed dotted violet in Figure 7) on the driver board may either be left open or equipped with a  $0\Omega$  jumper. In case of  $0\Omega$  the error outputs/inputs of the two SKYPER 42 LJ drivers are connected. In case R10 is not connected an error output of one driver would not be communicated to the error input of the other driver immediately.

SEMIKRON recommends to equip R10 with  $0\Omega$ .

#### Error handling of SKYPER 42 LJ PV

The 0805 sized resistors R15-R18 (framed dotted red in Figure 7) may be equipped as shown in Table 4 and Table 5. While R15 and R16 set the error handling for the driver of T1 and T2, R17 and R18 set the error handling for the driver of T3 and T4.

Any other combination (e.g. all resistors  $0\Omega$  or all resistors not connected) will lead to malfunction and may damage the system.

| Table 4: Functional table for R15 – R16 (error handling setup for T1 and T2) |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R15                                                                          | ΟΩ                                                                                                                                                                                                                                                                                                                                                                                                               | not equipped                                                                                                                                                                                                                                                                                                                                                     |

| R16                                                                          | not equipped                                                                                                                                                                                                                                                                                                                                                                                                     | Ω                                                                                                                                                                                                                                                                                                                                                                |

| Function →                                                                   | The particular driver generates an error<br>signal when a secondary side error occurs,<br>but the concerned IGBTs are not turned off.<br>The driver does not react to an external<br>error signal; it stays in the previous state<br>until it is turned off by PWM (in case of a<br>previous error, the soft-turn-off resistor is<br>used).<br>A continuous error signal prevents the<br>driver from turning on. | The particular driver generates an error signal and immediately turns off the concerned IGBTs using the soft-turn-off resistors when a secondary side error occurs.<br>In case an external error signal is applied the driver turns off the two IGBTs.<br>A continuous error signal prevents the driver from turning on.<br>⇒ <b>Default setup (recommended)</b> |

| Table 5: Functional table for R17 – R18 (error handling setup for T3 and T4) |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R17                                                                          | ΟΩ                                                                                                                                                                                                                                                                                                                                                                                                               | not equipped                                                                                                                                                                                                                                                                                                                                                     |

| R18                                                                          | not equipped                                                                                                                                                                                                                                                                                                                                                                                                     | ΩΩ                                                                                                                                                                                                                                                                                                                                                               |

| Function →                                                                   | The particular driver generates an error<br>signal when a secondary side error occurs,<br>but the concerned IGBTs are not turned off.<br>The driver does not react to an external<br>error signal; it stays in the previous state<br>until it is turned off by PWM (in case of a<br>previous error, the soft-turn-off resistor is<br>used).<br>A continuous error signal prevents the<br>driver from turning on. | The particular driver generates an error signal and immediately turns off the concerned IGBTs using the soft-turn-off resistors when a secondary side error occurs.<br>In case an external error signal is applied the driver turns off the two IGBTs.<br>A continuous error signal prevents the driver from turning on.<br>⇒ <b>Default setup (recommended)</b> |

#### Error input and error output of SKYPER 42 LJ PV

When error in- and outputs are connected to each other ( $R42=R47=0\Omega$ ), multiple drivers can share one error line. In this case one driver, that enters error mode, directly switches off the drivers connected to the same error line.

#### ⇒ Default setup (recommended)

With unconnected error in- and outputs it is possible to detect which driver board set the error. For that all error outputs have to be routed to the controller. The controller can then switch off other drivers by triggering the error input or deactivating input signals.

#### 3.4.8 Interlock time of driver T1/T2 and driver T3/T4

Interlock function has to be disabled since both IGBT T1 and T2 respectively T3 and T4 can be turned on at the same time.

| Table 6: Functional table for R19 – R20 (interlock setup for T3 and T4) |                                                                                                                                                          |                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R19                                                                     | 0Ω                                                                                                                                                       | not equipped                                                                                                                                                                                                       |

| R20                                                                     | not equipped                                                                                                                                             | 0Ω                                                                                                                                                                                                                 |

| Function →                                                              | The interlock time between T3 and T4 is set<br>to 0. That means that both IGBTs may be<br>switched on at the same time.<br>⇒ Default setup (recommended) | The interlock time between T3 and T4 is activated and set to $2\mu$ s. That means that one IGBT may be switched on $2\mu$ s after the other IGBT switched off. The two IGBTs cannot be turned on at the same time. |

| Table 7: Functional table for R21 – R22 (interlock setup for T1 and T2) |                                                                                                                                                          |                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R21                                                                     | 0Ω                                                                                                                                                       | not equipped                                                                                                                                                                                                       |

| R22                                                                     | not equipped                                                                                                                                             | 0Ω                                                                                                                                                                                                                 |

| Function →                                                              | The interlock time between T1 and T2 is set<br>to 0. That means that both IGBTs may be<br>switched on at the same time.<br>⇒ Default setup (recommended) | The interlock time between T1 and T2 is activated and set to $2\mu$ s. That means that one IGBT may be switched on $2\mu$ s after the other IGBT switched off. The two IGBTs cannot be turned on at the same time. |

#### **3.4.9** Input pulse filtering driver T1/T2 and driver T3/T4

The 0805 sized resistors R30-R33 (framed dotted red in Figure 7) may be equipped as shown in Table 8 and Table 9. R30 and R31 set the input pulse filtering function for the driver of T3 and T4, R32 and R33 set the input pulse filtering for the driver of T1 and T2.

Any other combination (e.g. all resistors  $0\Omega$  or all resistors not connected) will lead to malfunction and may damage the system.

| Table 8: Funct | Table 8: Functional table for R30 – R31 (Input pulse filtering for T3 and T4)                                                                                                              |                                                                                                                                                              |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R30            | 0Ω                                                                                                                                                                                         | not equipped                                                                                                                                                 |  |

| R31            | not equipped                                                                                                                                                                               | 0Ω                                                                                                                                                           |  |

| Function →     | The input pulse filtering is set to digital operation. The filter time is 375ns, delay time typically 0.7µs and the jitter 30ns with very low tolerances over the whole temperature range. | The input pulse filtering is set to analogue operation. The filter time is 180ns, delay time typically 0.4µs and the jitter 2.5ns.<br>⇒ <b>Default setup</b> |  |

| Table 9: Functional table for R32 – R33 (Input pulse filtering for T1 and T2) |                                                                                                                                                                                            |                                                                                                                                                              |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R32                                                                           | 0Ω                                                                                                                                                                                         | not equipped                                                                                                                                                 |

| R33                                                                           | not equipped                                                                                                                                                                               | 0Ω                                                                                                                                                           |

| Function →                                                                    | The input pulse filtering is set to digital operation. The filter time is 375ns, delay time typically 0.7µs and the jitter 30ns with very low tolerances over the whole temperature range. | The input pulse filtering is set to analogue operation. The filter time is 180ns, delay time typically 0.4µs and the jitter 2.5ns.<br>⇒ <b>Default setup</b> |

#### 4. User Interface

#### 4.1 Module interface